Taktgesteuerte Flipflops

Problemstellung:

Entwirf ein Bauteil, das sich eine Information (0 oder 1) merkt.

An einem Eingang a wird das Signal angelegt, das gespeichert werden soll.

An einem zweiten Eingang Takt (clock) wird durch ein kurzzeitiges Takt=0 ( ) signalisiert, dass der aktuelle Wert von a übernommen werden

soll.

) signalisiert, dass der aktuelle Wert von a übernommen werden

soll.

Lösung (zustandsgesteuert, taktpegelgesteuert)

Simulation mit Logisim (animiert)

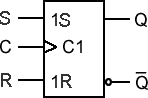

RS-Flipflop

Nachteil dieser Lösung: Solange der Takt C=0 ist, wird der Wert von a auf den Ausgang Q durchgeschaltet. Durch C=0 erfolgt also keine Momentaufnahme des Eingangs. Vielmehr steuert der Takt ein Tor, dass erst beim Übergang von 0 auf 1 (steigende Taktflanke  ) zugemacht wird.

) zugemacht wird.

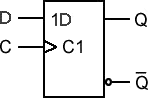

Erweiterung: D-Flipflop mit einem Eingang (zustandsgesteuert, taktpegelgesteuert)

Simulation mit Logisim

D-Flipflop

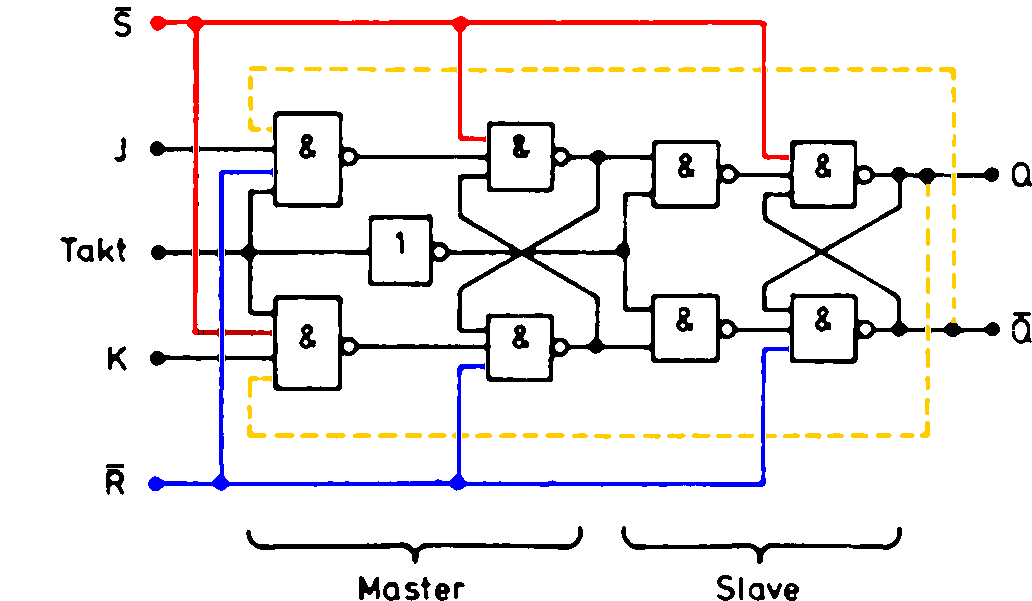

Taktflankengesteuerte Flipflops

Bei einem taktflankengesteuerten Flipflop erfolgt die Übernahme der Daten nur im Moment des Übergangs des Takteingangs von 1 auf 0 (also während der Taktflanke  ).

).

Simulation mit Logisim

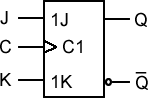

JK-Flipflop

Schalttafel für fallende Taktflanke

J K │ Q'

0 0 │ unverändert

0 1 │ 0 zurücksetzengesetzt

1 0 │ 1 gesetzt

1 1 │ wechselt (1 auf 0 bzw. 0 auf 1)